Page content last modified on 2025-04-04.

Our team is a part of the Computing Sciences

unit

at Tampere University, Finland. With over two decades of

experience, we've been at the forefront of media processing systems research. In close collaboration with

industry

leaders, we've developed innovative open-source solutions and datasets for video coding, processing, and

streaming. Our expertise covers a broad range, from optimizing low-power embedded devices to maximizing the

capabilities of expansive cloud environments.

Our open-source solutions:

All presented solutions are available on our github, or directly on our website (Datasets).

Kvazaar

our HEVC encoder

uvg266

our VVC encoder

uvgVPCCenc

our V-PCC encoder

UVG Dataset

our 4K dataset

UVG-VPC Dataset

our pointcloud dataset

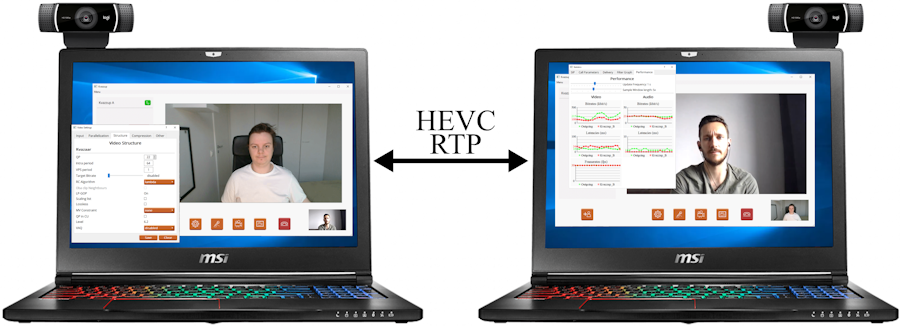

uvgRTP

our RTP library

CiThruS

our virtual city simulation

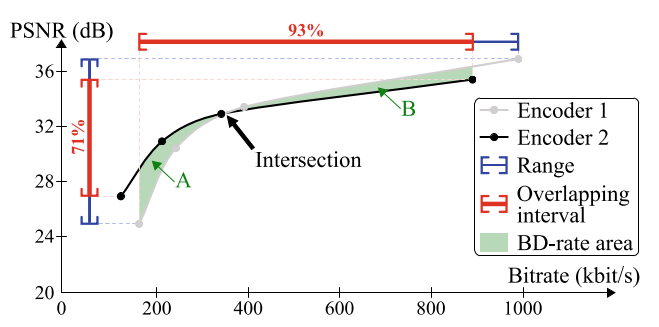

uvgVenctester

our video encoder testing framework

uvgComm

our video communication software

uvgKvazaarHW

our hardware HEVC intra encoder

Awards:

- 2025: Best Open Dataset and Software Paper at MMSys’25 for "uvgVPCCenc: Practical open-source encoder for fast V-PCC compression"

- 2024: Best Paper at VCIP 2024 for "Vectorized angular intra prediction for practical VVC encoding"

- 2023: Tampere University Open Science Promoter Award

- 2020: Best Open Dataset and Software Paper at MMSys’20 for "Kvazaar 2.0: fast and efficient open-source HEVC inter encoder"

- 2018: Best Poster at ICDCS 2018 for "Low Latency Edge Rendering Scheme for Interactive 360 Degree Virtual Reality Gaming"

- 2016: Winner of ACM Multimedia Open Source Software Competition

International and national projects involvement:

Contact Information:

You can contact us either using our mailing list (ultravideo[at]tuni.fi), by joining our Discord server or contacting us directly:- Head of the Group: Prof. Jarno Vanne

- Video Encoding & AI applications: Assist. Prof. Alexandre Mercat

- Hardware Development: Dr. Panu Sjövall

- AR/VR/XR Technologies: Dr. Guillaume Gautier